#### **REVISION HISTORY**

| REV | EDITOR                           | REVISION DESCRIPTION                                                          | APPROVAL | DATE     |

|-----|----------------------------------|-------------------------------------------------------------------------------|----------|----------|

| 1   | Nate Kemp                        | First Draft Version                                                           | TDK      | 12/17/02 |

| Α   | Troy Kopischke                   | Release                                                                       | TDK      | 01/27/03 |

| В   | Colette O'Brien                  | Release                                                                       | CRO      | 02/20/03 |

| С   | Kurt Larson                      | Release                                                                       | KTL      | 04/23/03 |

| D   | James Wicks                      | Added mode line description note                                              | JW       | 09/19/03 |

| Е   | James Wicks                      | Section 4.2.1 Edit                                                            |          | 11/05/03 |

| F   | Kurt Larson,<br>Michael Anderson | Signal characteristics update, Product Brief Section update                   | KTL      | 12/22/03 |

| G   | Kurt Larson<br>James Wicks       | Corrected SODIMM Pin Descriptions: 76, 78, 80; added bookmark feature to .pdf | JAW      | 09/30/04 |

| REV | EDITOR       | REVISION DESCRIPTION                                                                                         | SCHEMATIC<br>REV | APPROVAL | DATE     |

|-----|--------------|--------------------------------------------------------------------------------------------------------------|------------------|----------|----------|

|     |              | Updated Hirose PNs in Section 6.1 to reflect available parts;<br>Added second Important Note to Section 6.1; | 80000113         |          |          |

| Н   | Jed Anderson | General grammatical and formatting changes                                                                   | Rev F01          | JCA      | 11/03/06 |

Please check <u>www.logicpd.com</u> for the latest revision of this manual, errata's, and additional application notes.

This file contains source code, ideas, techniques, and information (the Information) which are Proprietary and Confidential Information of Logic Product Development, Inc. This information may not be used by or disclosed to any third party except under written license, and shall be subject to the limitations prescribed under license.

No warranties of any nature are extended by this document. Any product and related material disclosed herein are only furnished pursuant and subject to the terms and conditions of a duly executed license or agreement to purchase or lease equipments. The only warranties made by Logic Product Development, if any, with respect to the products described in this document are set forth in such license or agreement. Logic Product Development cannot accept any financial or other responsibility that may be the result of your use of the information in this document or software material, including direct, indirect, special or consequential damages.

Logic Product Development may have patents, patent applications, trademarks, copyrights, or other intellectual property rights covering the subject matter in this document. Except as expressly provided in any written agreement from Logic Product Development, the furnishing of this document does not give you any license to these patents, trademarks, copyrights, or other intellectual property.

The information contained herein is subject to change without notice. Revisions may be issued to advise of such changes and/or additions.

© Copyright 2006, Logic Product Development, Inc. All Rights Reserved.

# **Table of Contents**

| 1 |          | tion                                                           |    |

|---|----------|----------------------------------------------------------------|----|

|   | 1.1 Prod | duct Brief                                                     | 5  |

|   | 1.2 Acro | onyms                                                          | 6  |

|   | 1.3 Tec  | hnical Specifications                                          | 6  |

|   |          | d Engine Advantages                                            |    |

|   |          | d Engine Interface                                             |    |

|   |          | 9520-10 Card Engine Block Diagram                              |    |

|   |          | strical, Mechanical, and Environmental Specifications          |    |

|   | 1.7.1    |                                                                |    |

|   |          | Absolute Maximum Ratings                                       |    |

| _ | 1.7.2    | Recommended Operating Conditions                               |    |

| 2 |          | al Specification                                               |    |

|   |          | roController                                                   |    |

|   | 2.1.1    | LH79520 Microcontroller                                        |    |

|   | 2.1.2    | LH79520 Microcontroller Block Diagram                          |    |

|   |          | cks                                                            |    |

|   | 2.3 Mer  | nory                                                           | 13 |

|   | 2.3.1    | Synchronous Dynamic Random Access Memory (DRAM)                | 13 |

|   | 2.3.2    | Direct Memory Access (DMA)                                     |    |

|   | 2.3.3    | NOR Flash                                                      |    |

|   | 2.3.4    | CompactFlash (memory-mapped mode only)                         |    |

|   |          | 00 Ethernet Controller                                         |    |

|   |          | io CODEC                                                       |    |

|   |          | eo Interface                                                   |    |

|   |          | al Interface                                                   |    |

|   | 2.7.1    | UARTA                                                          |    |

|   | 2.7.2    | UARTB                                                          |    |

|   | 2.7.2    | SPI                                                            |    |

|   |          | ch Interface                                                   |    |

|   |          | neral Purpose Analog & Digital I/O                             |    |

|   |          | Controller                                                     |    |

|   |          |                                                                |    |

|   |          | al EEPROM Interface                                            |    |

| _ |          | ansion Options                                                 |    |

| 3 |          | Integration                                                    |    |

|   |          | figuration                                                     |    |

|   |          | ets                                                            |    |

|   | 3.2.1    | Master Reset (Hard Reset)                                      |    |

|   | 3.2.2    | Soft Reset                                                     |    |

|   |          | rrupts                                                         |    |

|   |          | G Debugger Interface                                           |    |

|   | 3.5 Pow  | ver Management                                                 | 20 |

|   | 3.5.1    | System Power Management                                        | 20 |

|   | 3.5.2    | Peripherals                                                    | 21 |

|   | 3.5.3    | Microcontroller                                                |    |

|   |          | O Considerations                                               |    |

| 4 |          | V & I/O Mapping                                                |    |

| • | •        | RAM Memory Map                                                 |    |

|   |          | ernal Static Memory Map                                        |    |

|   | 4.2.1    | Card Engine Static Memory Map Description                      |    |

|   | 4.2.1    | Chip Select 4 (nCS4) – IO Controller Peripherals (slow timing) |    |

|   | 4.2.2    | Chip Select 5 (nCS5) – 10 Controller Peripherals (slow timing) |    |

| F |          |                                                                |    |

| 5 |          | criptions & Functions                                          |    |

|   |          | Connector SODIMM 144-Pin Descriptions                          |    |

|   | 5.2 J1A  | Expansion Connector Pin Descriptions                           | 32 |

|   | 5.3 J1 | B Expansion Connector Pin Description     |    |

|---|--------|-------------------------------------------|----|

|   | 5.4 Mu | ultiplexed Signal Trade-Offs              | 37 |

|   |        | J1C Connector SODIMM 144-Pin Multiplexing |    |

|   |        | J1A Expansion Connector Pin Multiplexing  |    |

|   |        | J1B Expansion Connector Pin Multiplexing  |    |

| 6 |        | nical Specifications                      |    |

|   |        | erface Connectors                         | 30 |

# **LH79520 CARD ENGINE**

The LH79520 Card Engine is a compact, product-ready hardware and software solution for developing embedded products with less time, less cost, less risk ... more innovation.

#### **CARD ENGINE ADVANTAGE**

- Reduce Time to Market

- → 6 to 9 month savings typical

- Product-Ready Hardware Platform

- Production Quality Software

- Bootloader/Monitor

- Board Support Packages

- Supports other operating systems

- Engineering Support

The LH79520 Card Engine is a complete single board computer offering essential features for handheld and embedded networking applications in the industrial, consumer, and medical markets. The use of custom base boards makes the Card Engine the ideal foundation for OEMs developing handheld and compact products. The Card Engine provides a common reference pin-out on its expansion connectors, which enables customers to easily scale to next generation microcontroller Card Engines when new functionality or performance is required.

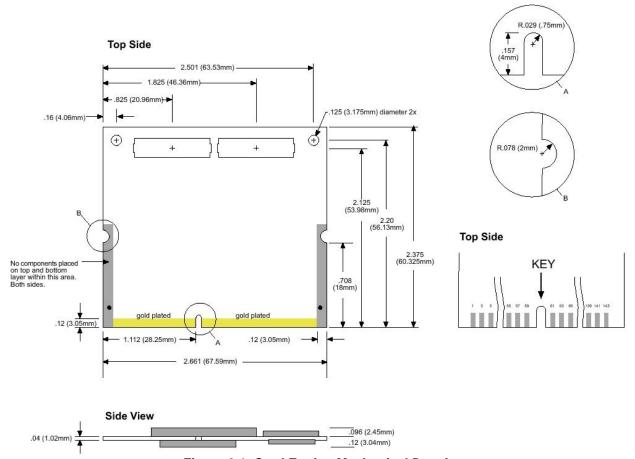

Actual Size (2.37" x 2.67")

- Processor Sharp LH79520 32 bit ARM720T RISC processor running up to 77.414 MHz

- SDRAM Memory Up to 64 Mbytes

- Flash Memory Up to 16 Mbytes on board

- **Display** Programmable color LCD controller

- Built in driver supports up to 800 x 600 x 16 bit color

- Supports STN, Color STN, HR-TFT, AD-TFT, TFT

- Touch Screen Four wire resistive touch controller

- Network Support 10/100 BASE-T Ethernet controller (application/debug)

- SMSC LAN91C111 (MAC & PHY)

- Audio Stereo Output Audio CODEC (TI TLV320DAC23)

- **PC Card Expansion** Compact Flash type 1 card (memory mode only)

- Serial Ports 2 X 16C550 like, standard UARTS

- IrDA SIR supports up to 115.2 Kbps

- **GPIO** Programmable depending on peripheral requirements

- SSP Supports either Motorola SPI™, National Semiconductor MICROWIRE™, TI SSI

- **USB 2.0 Full Speed** One Device

- Software

- Linux BSP

- LogicLoader™ (bootloader/monitor)

- Mechanical

- Compact Size: 2.37"(60.2 mm) long x 2.67"(67.8 mm) wide x 0.17"(4.4 mm) high

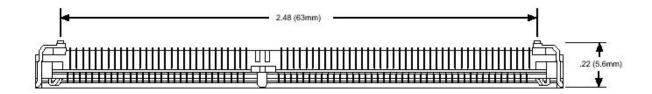

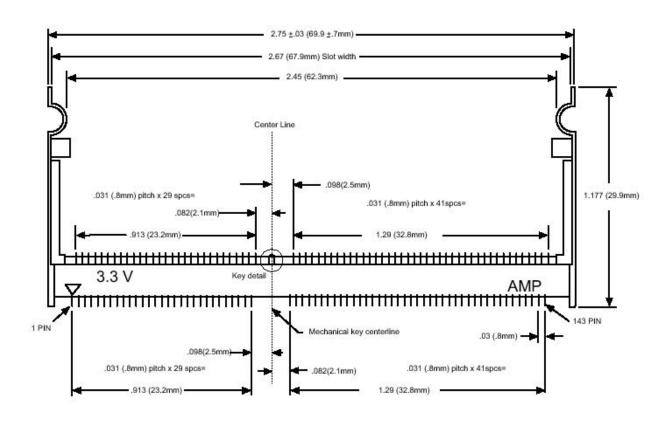

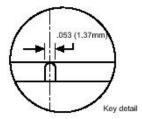

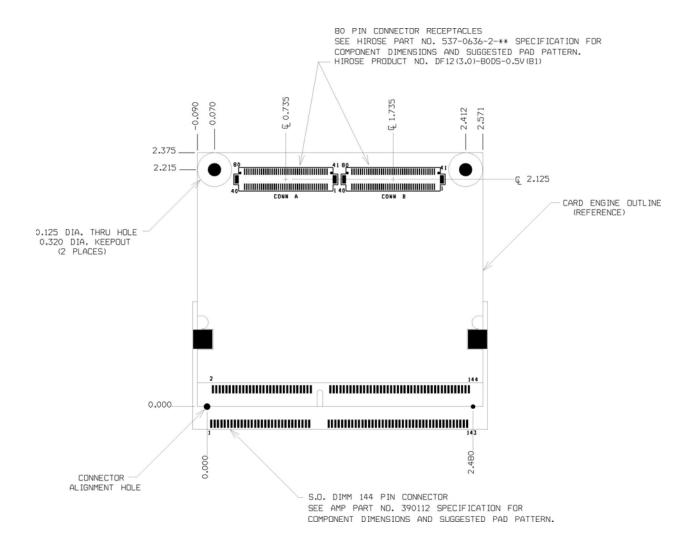

- 144 pin SODIMM connector for connection to custom peripheral board

- Two high density 80-pin expansion connectors for peripheral access

## **Application Development Kits**

- Zoom™ Starter Development Kit

#### **CUSTOMER SUPPORT**

Logic provides technical support for Application Development Kits. Various support packages are available; contact us for more information.

#### **CONTACT**

For more information on our EmbeddedProduct Solutions. please contact Logic Sales at www.logicpd.com or 612.672.9495.

## 1.2 Acronyms

ADC Analog to Digital Converter

AHB Advanced Hardware Bus

BSP Board Support Package

CPLD Complex Programmable Logic Device

DAC Digital to Analog Converter

DC Direct Current

DMA Direct Memory Access

DRAM Dynamic Random Access Memory

ENDEC Encoder Decoder

ESD Electro Static Dissipative

FET Field Effect Transistor

FIQ Fast Interrupt Request

GPIO General Purpose Input Output

HAL Hardware Abstraction Layer

IC Integrated Circuit

IO Input Output

LCD Liquid Crystal Display

LOLO LogicLoader<sup>TM</sup>

NC No Connect

PLL Phase Lock Loop

PMOS P Metal Oxide Semiconductor

RTC Real Time Clock

SDRAM Synchronous Dynamic Random Access Memory

SSP Synchronous Serial Port TTL Transistor Transistor Logic

UART Universal Asynchronous Receive Transmit

VIC Vectored Interrupt Controller

### 1.3 Technical Specifications

Please refer to the following component specifications and data sheets.

LH79520-10 IO Controller Interface Specification

LogicLoader™ User's Manual

LH79520 Universal Microcontroller User's Guide Altera MAX 7000A CPLD data sheet (EPM7128A)

Altera Device Package Information data sheet

Altera Ordering Information

Texas Instruments TLV320DAC23 data manual

Texas Instruments (Burr-Brown) ADS7843 data sheet

## 1.4 Card Engine Advantages

Logic's Card Engines accelerate your products time to market. In addition, the Card Engines provide the following advantages:

- Product Ready Hardware & Software solutions allow immediate application development which results in embedded product development cycle with less time, less cost, less risk, with more innovation.

- Less time time to market solution allows software application development to begin immediately

- □ Less cost significantly lowers development cost

- □ Less risk complex portion of design product ready

- ☐ More Innovation Allows you to focus on your IP

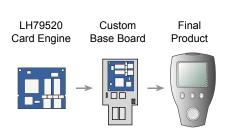

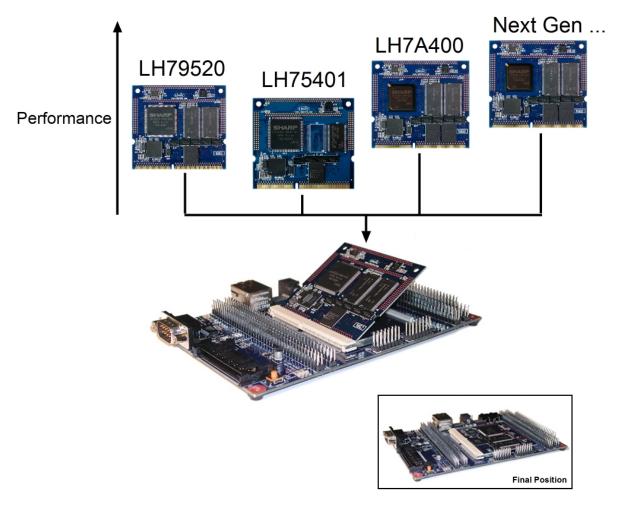

- Common Card Engine Footprint (See Figure 1.1)

- □ Easy migration path to new processors and technology

- Provides a scaleable solution for your product family

- □ Extends product life cycle worry free component obsolescence

- Low Cost Hardware Solution Custom configurations to meet your design requirements and price points.

- Complex portion of the design complete and ready to go.

## 1.5 Card Engine Interface

The Card Engine's common interface allows you to easily migrate to new processors and technology. Logic is in constant research and development of new technologies to improve performance, lower cost and increase feature capabilities. By using the common footprint, you can leverage Logic's work without having to re-spin your product. Contact Logic sales for more information.

Figure 1.1: Card Engine Advantages

Encapsulating a significant amount of your design onto the Card Engine reduces risk of obsolescence issues. If a component on the Card Engine design becomes obsolete you don't have to re-spin your board, Logic will design for alternative part that is transparent to your product. Manufacturing also becomes much easier. Card Engines are delivered to you fully tested, making your manufacturing process simpler and less costly.

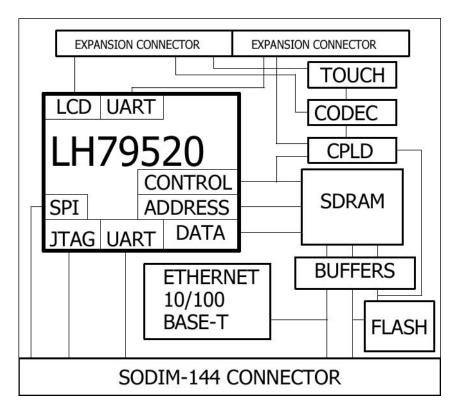

## 1.6 LH79520-10 Card Engine Block Diagram

Figure 1.2: LH79520-10 Card Engine Block Diagram

## 1.7 Electrical, Mechanical, and Environmental Specifications

## 1.7.1 Absolute Maximum Ratings

| Parameter                           | Symbol | Rating      | unit |

|-------------------------------------|--------|-------------|------|

| DC IO and Peripheral Supply Voltage | 3.3V   | -0.3 to 4.6 | V    |

| DC Core Supply Voltage              | VCORE  | -0.3 to 2.4 | V    |

NOTE: These stress ratings are only for transient conditions. Operation at or beyond absolute maximum rating conditions may affect reliability and cause permanent damage to the Card Engine and its components.

## 1.7.2 Recommended Operating Conditions

| Parameter                        | Min  | Typical    | Max  | Unit   | Notes |

|----------------------------------|------|------------|------|--------|-------|

| DC IO and Peripheral Supply      | 3.0  | 3.3        | 3.6  | V      | 1     |

| Voltage                          |      |            |      |        |       |

| DC IO Supply Active Current      | TBD  | 240        | TBD  | mA     | 2     |

| DC IO Supply Standby Current     | TBD  | 180        | TBD  | mA     | 2     |

| DC IO Supply Sleep Current       | TBD  | 130        | TBD  | mA     | 2     |

| DC Core Supply Voltage           | 1.62 | 1.8        | 1.98 | V      | 1     |

| DC Core Supply Active Current    | TBD  | 40         | TBD  | mA     | 2     |

| DC Core Supply Standby Current   | TBD  | 30         | TBD  | mΑ     | 2     |

| DC Core Supply Sleep Current     | TBD  | 0          | TBD  | mA     | 2     |

| Commercial Operating Temperature | 0    | 25         | 70   | °C     |       |

| Industrial Operating Temperature | -40  | 25         | 85   | °C     | 3     |

| Storage Temperature              | -40  | 25         | 85   | °C     |       |

| Dimensions                       |      | 2.35 x 2.6 |      | Inches |       |

| Weight                           |      | 17         |      | Grams  | 4     |

| Connector Insertion/removal      |      | 50         |      | Cycles |       |

| Input signal High Voltage        |      | 2.0        |      | V      |       |

| Input Signal Low Voltage         |      | 8.0        |      | V      |       |

| Output Signal High Voltage       | 2.6  |            | VIO  | V      |       |

| Output Signal Low Voltage        | GND  |            | 0.4  | V      |       |

- 1. Core voltage must never exceed IO and peripheral supply voltage.

- 2. This test was performed with the 91C111 chip power disabled.

- 3. Contact Logic for more information on an industrial temperature LH79520-10 Card Engine

- 4. May vary depending on Card Engine configuration.

## 2 Electrical Specification

#### 2.1 MicroController

#### 2.1.1 LH79520 Microcontroller

The LH79520-10 Card Engine uses Sharp's highly integrated system on a chip LH79520 microcontroller. Sharp's LH79520 has a 32-bit ARM720T RISC core. Sharp's LH79520 microcontroller is a system on a chip providing many integrated on-chip peripherals including:

- Integrated ARM720T<sup>TM</sup> Core

- □ 2 bit ARM7TDMI™ RISC Core

- 8 KB Cache

- MMU

- 32 KB on-chip SRAM

- Integrated LCD Controller

- □ Up to 800 x 600 Resolution

- □ Supports STN, TFT, HR-TFT

- □ 64 k Colors

- Three UART's

- IrDA SIR up to 115.2 Kbps (UART0)

- SPI (UART2)

- Up to 64 General Purpose I/O Signals

- Two 16-bit Pulse Width Modulators

- Four DMA Channels (2 External)

- Four Counter/Timers

- RTC

- Low Power Modes

- 5 Volt Tolerant Inputs

See Sharp's LH79520 Universal Microcontroller User's Guide for additional information. <a href="http://www.sharpsma.com/">http://www.sharpsma.com/</a>

**IMPORTANT NOTE:** Please see <a href="http://www.sharpsma.com/">http://www.sharpsma.com/</a> for any errata on the LH79520.

## 2.1.2 LH79520 Microcontroller Block Diagram

Figure 2.1: LH79520 Microcontroller Block Diagram

#### 2.2 Clocks

The LH79520 uses a 14.7456 MHz crystal, which is scaleable in software to generate FCLK signal. FCLK is used internally for the ARM720T core and cache. The 14.7456 MHz crystal is also used to generate HCLK that is used to generate other bus and peripheral clocks. The 32.768 kHz crystal is used for the RTC interface.

The LH79520 is software configurable to select between asynchronous, synchronous, and FastBus extension clocking mode. The microcontroller has a sophisticated clocking architecture and can be software programmable tailored to an application to vary the microcontroller performance, power consumption, and bus throughput. See the LH79520 Universal Microcontroller User's Guide for more details.

The LH79520's microcontroller core clock speed is initialized to 51.6096 MHz on the Card Engine and the Bus speed is 51.6096 MHz in the LogicLoader<sup>TM</sup>. Other clock speeds can be supported and modified in software for specific user applications, such as a specific serial baud rate.

The LH79520-10 Card Engine provides an external Bus clock, uP\_BUS\_CLK, on the 144-pin SO-DIMM connector. The uP\_BUS\_CLK, the LH79520 Bus clock – SDCLK, is set to a default of 51.6096 MHz. The uP\_BUS\_CLK signal is programmable via the LH79520 clock registers.

The LH79520-10 Card Engine provides an external auxiliary clock, uP\_AUX\_CLK, on the 144-pin SO-DIMM connector. The uP\_AUX\_CLK, the LH79520 CLKOUT, is set to a default of 51.6096 MHz. The uP\_AUX\_CLK signal is programmable via the LH79520 clock registers.

| LH79520 Microcontroller<br>Signal Name | LH79520-10 Card Engine<br>Net Name | Default Software Value in<br>LogicLoader™ |

|----------------------------------------|------------------------------------|-------------------------------------------|

| FCLK                                   | NA                                 | 51.6096 MHz                               |

| HCLK                                   | NA                                 | 51.6096 MHz                               |

| SDCLK                                  | uP_BUS_CLK                         | 51.6096 MHz                               |

| CLKOUT                                 | uP_AUX_CLK                         | 51.6096 MHz                               |

## 2.3 Memory

## 2.3.1 Synchronous Dynamic Random Access Memory (DRAM)

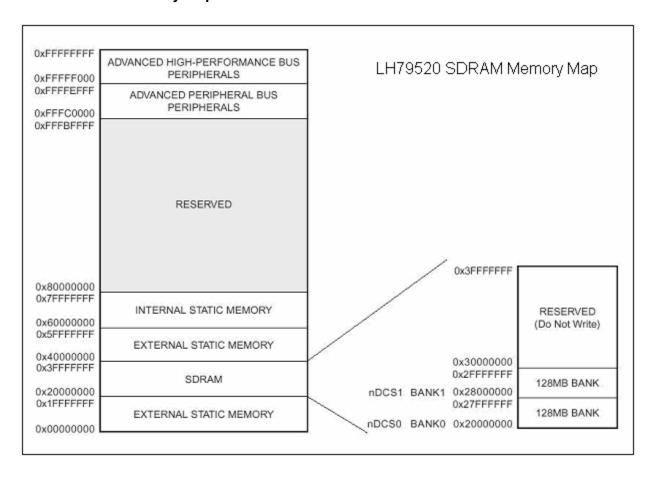

The LH79520-10 Card Engine uses a 32-bit memory bus to interface to Synchronous DRAM. The memory can be configured as 16, 32 or 64 Mbytes to meet the user's memory requirements and cost constraints. The default memory configuration is a 32 Mbyte configuration.

#### 2.3.2 Direct Memory Access (DMA)

The Sharp LH79520 microcontroller has an internal DMA controller and 2 external DMA channels. The standard LH79520-10 Card Engine uses DMA Channel 0 to interface with the onboard audio CODEC - Texas Instruments TLV320DAC23. The DMA channel 1 DREQ signal is multiplexed with the LH79520 nWAIT signal. By default, the nWAIT signal is used to interface with the onboard Ethernet controller - SMSC 91C111. DMA Channel 1 is available to the user through the expansion connectors if the user chooses to not use the nWAIT signal in the SMSC 91C111 Ethernet controller. The SMSC 91C111 can be configured in software to exclude the nWAIT signal functionality, providing DMA Channel 1 to the user. If an external DMA channel is required, please contact Logic Product Development.

#### 2.3.3 NOR Flash

The LH79520-10 Card Engine uses a 16-bit memory bus to interface to Strataflash. The on board Card Engine memory can be configured as 8 or 16 Mbytes to meet the user's flash requirements and cost constraints. A user should consult Logic when specifying flash size because it is one of the most expensive components in the LH79520-10 Card Engine.

A user can expand their non-volatile storage capability using the LH79520-10 Card Engine Application Kit as a design reference. User's can expand their non-volatile storage capability by external flash ICs, CompactFlash, or NAND Flash. See the LH79520-10 Application Kit for reference designs or contact Logic for other reference designs of peripheral interfaces.

#### 2.3.4 CompactFlash (memory-mapped mode only)

The LH79520 microcontroller does not have an on chip integrated CompactFlash controller. However, for applications requiring larger non-volatile storage, the LH79520-10 Card Engine provides the necessary signals using the IO Controller for a CompactFlash card interface in memory-mapped mode only. The Zoom<sup>TM</sup> Starter Kit reference design includes a CompactFlash

connector for memory-mapped mode, but does not support the hot-swappable capability. See the LH79520-10 IO Controller Interface Specification for further details.

Logic PN: 70000014

**IMPORTANT NOTE:** Additional hardware is required on the user's daughter board to provide hot-swapping capability.

**IMPORTANT NOTE:** The IO Controller CompactFlash interface supports memory-mapped mode only. Designs requiring other CompactFlash modes should use an external controller or select a microcontroller with an integrated CompactFlash interface.

### 2.4 10/100 Ethernet Controller

The LH79520-10 Card Engine uses the SMSC 91C111 10/100 Ethernet single chip solution. The Card Engine Ethernet interface provides an easy to use interface. The Card Engine provides six signals from the 91C111: TPO+, TPO-, TPI+, TPI-, ACT\_LED, and LNK\_LED. The four analog PHY interface signals (TPO+, TPO-, TPI+, TPI-) require an external impedence matching circuit. Logic provides an example circuit schematics in the LH79520-10 Application Kit for reference.

**IMPORTANT NOTE:** Eneep signal on the SMSC 91C111 is connected to npR15 (zero ohm resistor) that is not populated. Eneep signal has an internal weak pull up in the SMSC 91C111. If Eneep signal is tied low it will disable the serial EEPROM interface.

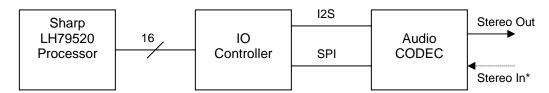

#### 2.5 Audio CODEC

The LH79520-10 Card Engine uses the TI TLV320DAC23GQE high performance low cost stereo audio CODEC. The TLV320DAC23GQE audio CODEC has a single channel stereo input and single channel stereo output, but the LH79520-10 Card Engine does not support stereo input on its standard card engine.

Figure 2.2: Audio CODEC Block Diagram

#### \*IMPORTANT NOTE: Stereo In not supported in default LH79520-10 Card Engine

The LH79520-10 Card Engine supports a 10-bit stereo out. The audio CODEC uses a 5.6448 MHz crystal. The audio CODEC is software programmable via the SPI interface in the IO Controller. See the IO Controller Interface Specification for programming information. The audio CODEC provides software programmable sample rates, volume control, mute, and power management. See the TI Audio CODEC specification for programmable register settings.

Logic has interfaced other high performance audio CODECs to the Card Engines. Contact Logic for assistance in selecting an appropriate audio CODEC for your application.

### 2.6 Video Interface

Sharp's LH79520 microcontroller has a built in LCD controller supporting STN, TFT, HR-TFT panels at 800 x 600 x 16 bit color max resolution. See the LH79520 Universal Microcontroller User's Guide for further information on the integrated LCD controller. The LCD controller signals from the LH79520 are located on one of the Card Engine's 80-pin expansion connectors. Logic

has written drivers for numerous panels of different types and sizes. Please contact Logic before selecting a panel for your application.

**IMPORTANT NOTE:** Using the internal graphics controller will effect processor performance. Selecting display resolutions and color bits per pixel will vary processor bus load.

## 2.7 Serial Interface

The LH79520-10 Card Engine comes with the following serial channels: UARTA, UARTB, and SPI. If additional serial channels are required, please contact Logic for reference designs. UARTB includes a Serial InfraRed (SIR) ENDEC (Encoder/Decoder), and is capable of generating two interrupts not available from UARTA or the SPI.

#### 2.7.1 **UARTA**

UARTA has been configured to be the LH79520 main serial port. It is an asynchronous 16C550 compatible UART. This SCIF interface is a high-speed serial interface with a FIFO (asynchronous or synchronous) and is capable of sending and receiving serial data simultaneously. The signals from the Card Engine are TTL level signals not RS232 level. The user must provide an external RS232 transceiver for RS232 applications. Logic has provided an example reference design with the Zoom™ Starter Kit. When choosing an RS232 transceiver, the user should keep in mind cost, availability, ESD protection, and data rates.

UARTA's baud rate is set by default to 115.2K bits/sec, though it supports all common serial baud rates from 110bps to 460.8K bits/sec. UART A is available off the 144-pin SO-DIMM connector. Please see the LH79520 Universal Microcontroller User's Guide for further information.

#### 2.7.2 **UARTB**

Serial Port UARTB has dual functionality, its primary function is as an asynchronous 16C550 compatible UART. This SCIF interface is also a high-speed serial interface with a FIFO (asynchronous or synchronous) and is capable of sending and receiving serial data simultaneously. The signals from the Card Engine are TTL level signals not RS232 level. The user is responsible for providing an external RS232 transceiver for RS232 applications. UARTB's baud rate can also be set to all common serial baud rates from 110bps to 460.8K bits/sec.

UARTB's secondary function is as an IrDA-compatible Serial InfraRed (SIR) Encoder/Decoder (ENDEC) block that supports serial infrared communications. The SIR ENDEC can be enabled for serial IR communication through pins uP\_UARTB\_TX - IR and uP\_UARTB\_RX - IR. The SIR ENDEC is half-duplex only, so it cannot receive while transmitting, or transmit while receiving. UART B/IrDA port is available off one of the 80 pin expansion connectors. Please see the LH79520 Universal Microcontroller User's Guide for further information.

#### 2.7.3 SPI

The SPI interface on the LH79520 is a SSP (synchronous serial port) used to facilitate synchronous serial communications with slave peripheral devices. This serial port is a Master-only device, with programmable clock bit-rate and prescale factors. It supports three data frame formats:

- Texas Instruments' SSI

- Motorola SPI™

- National Semiconductor Microwire<sup>TM</sup>

The SPI interface signals are available off the 144-pin SO-DIMM connector. Please see the LH79520 Universal Microcontroller User's Guide for further information.

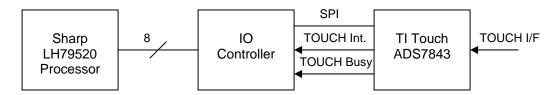

### 2.8 Touch Interface

Touch interface is supported on the LH79520-10 Card Engine for standard 4-wire resistive touch panels. The LH79520-10 Card Engine implements the popular TI ADS7843 12-bit sampling ADC touch controller. See the ADS7843 specification for more detailed information. The touch controller interfaces to the LH79520 microcontroller through the IO Controller, which provides a parallel to SPI interface. Why not use the SPI interface provided on the LH79520 microcontroller? Many of Logic's customers use the on-chip (microcontroller) SPI port for their applications, therefore Logic designs their Card Engines to keep the serial channels free for user applications.

Figure 2.3: Touch Controller Block Diagram

The IO Controller Interface Specification provides the necessary information to interface to the touch controller. Please see the LH79520-10 Card Engine IO Controller Interface Specification for more information.

## 2.9 General Purpose Analog & Digital I/O

Logic designed the LH79520-10 Card Engine to be flexible and provided multiple options for analog and digital GPIO. There are numerous digital GPIO on the Card Engine that interface to the LH79520, and the IO Controller. Some of these GPIO are interrupt capable while other signals are input or output only. Please see the Pin Descriptions section of this data sheet. The LH79520 microcontroller does not contain an internal Analog to Digital Converter (ADC), however, the ADS7843 Touch Chip (U12) provides 2 analog inputs available to the user. The IO Controller Interface Specification provides a user with the necessary information to interface to the touch controller. Please see the IO Controller Interface Specification for more information. If certain peripherals are not used, such as the LCD Controller, Chip Selects, IRQs, UARTs, or SPI port multiple GPIO pins become available. Please see the table in section 5 entitled "Multiplexed Signal Trade-Offs." This table lists the available GPIO trade-offs that are available when certain peripheral functions are not used.

#### 2.10 IO Controller

Please see the LH79520-10 Card Engine IO Controller Interface Specification for more information.

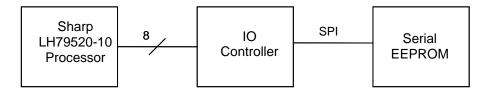

#### 2.11 Serial EEPROM Interface

Logic designed the LH79520-10 Card Engine to have a low cost 1 kbit serial EEPROM for non-volatile data storage. The serial EEPROM is connected to the LH79520 microcontroller via the IO Controller through an SPI interface. See Figure 2.4 below. Please see the LH79520-10 Card Engine IO Controller Interface Specification for more information.

Figure 2.4: Serial EEPROM Block Diagram

## 2.12 Expansion Options

The LH79520-10 Card Engine was designed for expansion and provides all the necessary control signals and bus signals to expand the user's design. Many of these signals are buffered and brought out to the 144-pin SO-DIMM connector and two 80 pin expansion connectors. See the LH79520-10 Card Engine schematics for more detail. A user can expand the Card Engine's functionality such as PCI, CompactFlash, PCMCIA, ISA devices, PCI devices, etc.. Logic has expanded the Card Engine to other audio CODECs, Ethernet IC's, UARTs, Co-processors, etc. Please contact Logic for potential reference designs before selecting your peripherals.

## 3 System Integration

## 3.1 Configuration

The LH79520-10 Card Engine was designed to be configurable to meet user's applications and budget needs. The Card Engine supports a variety of embedded operating systems and comes in the following hardware configurations:

- Flexible memory footprint: 16, 32, or 64 Mbytes Synchronous DRAM

- Flexible flash footprint: 8 or 16 Mbytes StrataFlash

- Optional SMSC 91C111 10/100 Ethernet Controller

- Optional TI TLV320DAC23GQE Audio CODEC

- Optional Touch Controller

Please contact Logic for additional hardware configurations to meet your application.

#### 3.2 Resets

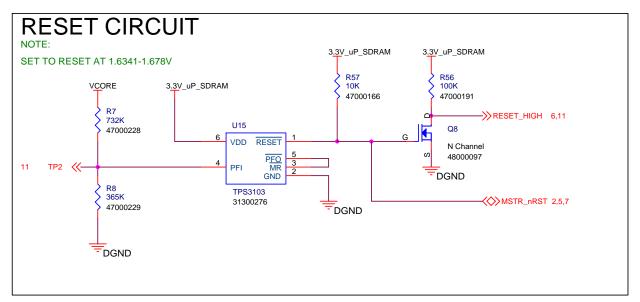

#### 3.2.1 Master Reset (Hard Reset)

Any microcontroller or peripheral having a hardware-reset signal is reset by the MSTR\_nRST or RESET\_HIGH signal. MSTR\_nRST should be the "pin hole" reset used for commercial embedded systems implemented with the LH79520-10 Card Engine. If MSTR\_nRST is asserted, the user can expect to lose information stored in SDRAM.

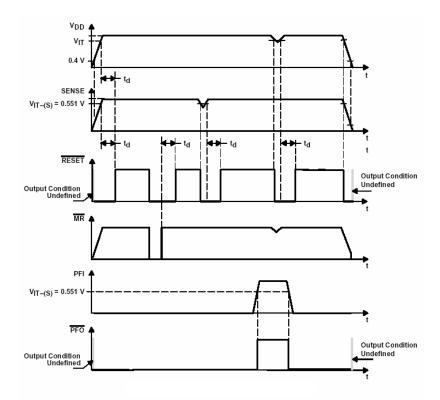

Figure 3.1: Reset Circuit

The MSTR\_nRST signal is an active low output of the reset chip, located on the card engine. The RESET\_HIGH signal is an active high signal.

**IMPORTANT NOTE:** The user should guard the assertion of the reset lines during a low power state so the microcontroller cannot be reset and powered up with bad power (will cause data corruption and possible temporary system lockup). See section entitled "Power Management" for further details. The timing diagrams for the reset chip are shown in Figure 3.2.

Figure 3.2: Reset IC Timing Diagram

There are three conditions that will generate a low on the output reset pin of the reset chip (the MSTR\_nRST signal): power-on condition, a low pulse on the MSTR\_nRST signal, and the power fail comparator input (PFI pin) falling below the internal comparator threshold.

#### Power On:

At power on, MSTR\_nRST signal is asserted low when the supply voltage (VDD) of the reset chip becomes higher than 1.1V. Once VDD signal becomes higher than 2.93V, an internal timer will delay the rising edge of MSTR nRST for 200 ms (typical).

## Low Pulse on MSTR\_RST Signal:

A low pulse on the MSTR\_nRST signal of the reset chip, asserted by a push button located on the application board, will bring MSTR\_nRST low. MSTR\_nRST will return high as soon as it is deasserted offboard.

#### Power Fail:

If the power fail comparator input pin (PFI pin) falls below the internal comparator threshold of 1.25V, it will create a low pulse on the MR input pin of the reset chip (after a delay of 0.5 uS). The MSTR\_nRST pin will then follow the above stated procedure for a low pulse on the MR pin.

**IMPORTANT NOTE:** It is critical that a user is careful in selecting cross-parts for the reset IC. The current reset chip in the BOM has an open drain output for output pin RESET. Other cross-parts may not have an open drain on this pin and will fail when MSTR\_nRST signal is asserted to GND.

#### 3.2.2 Soft Reset

Logic has created a soft reset signal named uP\_SW\_nRESET that can be used to reset the LH79520 internal registers, without affecting the peripherals on the rest of the board and without losing data stored in SDRAM or other volatile storage. The uP\_SW\_nRESET signal is an input to

the IO Controller. When a low pulse is detected, the IO Controller generates an interrupt to the microcontroller. The microcontroller then reads the interrupt/mask register of the IO Controller, which indicates a soft reset has been administered.

## 3.3 Interrupts

The LH79520 responds to ARM exceptions and vectored interrupts generated by the onboard-vectored interrupt controller (VIC). The LH79520 accepts inputs from 32 interrupt sources--24 are from internal sources, and 8 are from external sources. All interrupts are routed to the VIC where priorities are determined by hardware and the appropriate interrupt signal is dispatched to the ARM720T exception-handling hardware. Lower numbered interrupts have higher priority than higher-numbered interrupts. Each external interrupt has rising edge, falling edge, HIGH level, or LOW-level trigger options. The LH79520-10 Card Engine interrupts are set to trigger on a LOW level by default. The LH79520-10 Card Engine provides 7 available interrupt sources. Each of the interrupts can be separately setup as FIQs via software. Refer to Sharp's LH79520 Universal Microcontroller User's Guide for further information.

| LPD Signal | LH79520 Signal | External User Availability          | Default Use                 |

|------------|----------------|-------------------------------------|-----------------------------|

| uP_NMI     | INT0           | Available                           |                             |

| uP_IRQA    | INT1           | Available                           |                             |

| uP_IRQB    | INT2           | Available                           |                             |

| uP_IRQC    | INT3           | Available                           |                             |

| uP_IRQ4    | INT4           | Not Available                       | Onboard IO Controller (U11) |

| uP_nWAIT   | INT5           | Available if uP_WAIT# is not used   | Onboard Ethernet (U10)      |

| G4         | INT6           | Available if LCD signal is not used | Offboard LCD Display        |

| G5         | INT7           | Available if LCD signal is not used | Offboard LCD Display        |

**IMPORTANT NOTE:** See LH79520-10 Card Engine IO Controller Interface Specification for detailed information on the use of the uP\_IRQ4 interrupt.

## 3.4 JTAG Debugger Interface

There are many different third party JTAG debuggers available for Sharp ARM microcontrollers. The JTAG connection enables a user to recover a board that has corrupted flash memory and to debug real time applications. The following signals make up the JTAG interface to the LH79520, for connection to an JTAG emulator: uP\_TRST, uP\_TDI, uP\_TMS, uP\_TCK, uP\_TDO. These signals should interface directly to a 20-pin or 14-pin 0.1" through-hole connector as demonstrated in the Sharp LH79520 Universal Microcontroller User's Guide, or as shown on reference schematics.

**IMPORTANT NOTE:** When laying the 20-pin or 14-pin connector out, realize it may not be numbered as a standard 20-pin or 14-pin 0.1" IDC through-hole connector. See LH79520-10 Card Engine Application Kit reference design for further details. Different IC manufacturers define the 20-pin or 14-pin IDC connector pin-out differently.

## 3.5 Power Management

## 3.5.1 System Power Management

Good power management design happens in the hardware and software of any system. Typically, the power management design of any embedded system can be one of the most complicated parts and has a dramatic effect on the overall product cost, performance, usability, and customer satisfaction. Many factors effect good power management design in the hardware including: power supply selection (efficiency), clocking design, IC and component selection, etc.

The LH79520-10 Card Engine electronics were designed to provide maximum flexibility to the software and system integrator.

Logic PN: 70000014

There are many different software configurations which drastically effect the power consumption of the LH79520-10 Card Engine including: microcontroller core clock frequency, microcontroller bus clock frequency, microcontroller peripheral clocks, microcontroller bus modes (asynchronous, synchronous, FastBus), microcontroller power management states (active, standby, sleep, stop1, stop2), peripheral power states and modes, product user scenarios, interrupt handling, display settings (resolution, backlight, refresh, bits per pixel, etc..) These settings are typically initialized in the startup software routines and may be later modified in the operating system and application software. These items are covered in the appropriate documents such as the LogicLoader™ User's Manual or appropriate BSP manual.

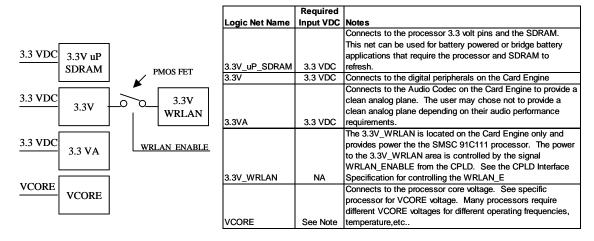

The LH79520-10 Card Engine was designed to have the following five power areas, 3.3V\_uP\_SDRAM, 3.3V, 3.3VA, and VCORE for a flexible hardware design. See Figure 3.3 below.

Figure 3.3: Power Plane Diagram

**IMPORTANT NOTE:** The purpose of the PMOS FET to control the power to the SMSC 91C111 is because the software power management in the 91C111 is not suitable for many applications.

**IMPORTANT NOTE:** The 3.3V\_WRLAN signal is an output from the card engine and is used to power off board Wired Lan related circuitry. Typically this signal is used to power Activity and Link status LEDs.

**IMPORTANT NOTE**: The LH79520-10 Card Engine hardware architecture was designed for low power battery operated applications. However, the Altera CPLD on the LH79520-10 Card Engine is not an ideal part for low power battery operated designs. This specific component was chosen for cost. If one is using the LH79520-10 Card Engine as a reference design, one can consider other programmable logic devices that are optimized for power, not cost.

#### 3.5.2 Peripherals

Most peripherals provide software programmable power states. The audio CODEC and touch controller have programmable power states. Please see the appropriate data sheet for more information and the IO Controller Interface Specification for details. The SMSC 91C111 controller has software programmable power states but may not be sufficient for some applications. Logic has provided hardware to cut power to the 91C111 IC.

#### 3.5.3 Microcontroller

The LH79520-10 Card Engine power management's scheme was designed to be easy to use. There are five power management states provided in the LH79520 microcontroller: ACTIVE, STANDBY, SLEEP, STOP1, and STOP2. Sharp's LH79520 provides complex power management features. Please see the LH79520 Universal Microcontroller User's Guide for more details.

**IMPORTANT NOTE:** The BSPs available from Logic for the different operating systems supported on the LH79520 may not support all five of the power management states. Please see the appropriate BSP documentation for power management modes for more detail.

#### 3.5.3.1 Active Mode

The LH79520-10 Card Engine normal operating state is ACTIVE. The LH79520 system on a chip enters this mode on reset and returns to this mode when any interrupt is received, if operating in any other power mode. The LH79520 cannot transition directly between the other power modes; it will always return to active mode before entering any other power mode.

### 3.5.3.2 Standby Mode

The Standby mode halts the clocks to the CPU while leaving the remainder of the chip active. The LH79520 transitions from the Standby mode to the Active mode when an interrupt is received.

#### 3.5.3.3 Sleep Mode

The Sleep mode halts all system clocks. Only the PLL and the internal oscillators remain active. If the 32.768 kHz internal oscillator is in use, it will also remain active. The LH79520 transitions from the Sleep mode to the Active mode when an interrupt is received.

When transitioning from the Active mode to the Sleep mode, the LH7920 Power Management system automatically performs the following sequence:

- Acquires control of the AHB, to ensure that all transactions are completed.

- Ensures that all SDRAM devices are placed in the self-refresh mode of operation.

- Halts all output clocks that are driven by HCLK, HCLK CPU, and PCLK

- Waits for IRQ or FIQ to be asserted (which will return the LH79520 to the Active mode).

When an IRQ or FIQ occurs, the LH79520 returns to the Active mode, restarts the output clocks, resumes SDRAM refresh and then cedes control of the AHB.

#### 3.5.3.4 Stop1 Mode

The Stop1 mode halts all system clocks and disables the PLL but keeps the internal oscillators active. If the 32.768 kHz internal oscillator is in use, it will remain active. The LH79520 transitions from the Stop1 mode to the Active mode when an interrupt is received.

When transitioning from the Active mode to the Stop1 mode, the LH79520 Power Management system automatically performs the following sequence:

- Acquire control of the AHB, to ensure that all transactions are completed.

- Ensure that all SDRAM devices are placed in the self-refresh mode of operation.

- Halts all clocks, disable the PLL and deassert the CLKEN output signal.

- Wait for IRQ or FIQ to be asserted (which will return the LH79520 to the Active mode).

When an IRQ or FIQ occurs, the LH79520 returns to the Active mode, restarts the output clocks (which may require a delay for the PLL to reacquire lock, if the PLL is in use), resumes SDRAM refresh and then cedes control of the AHB.

#### 3.5.3.5 Stop2 Mode

The Stop2 mode halts all system clocks and disables both the PLL and the internal oscillators that feed it. If the 32.768 kHz internal oscillator is in use, it will remain active. The LH79520 transitions from the Stop2 mode to the Active mode when an interrupt is received.

When transitioning from the Active mode to the Stop2 mode, the LH79520 Power Management system automatically performs the following sequence:

- Acquire control of the AHB, to ensure that all transactions are completed.

- Ensure that all SDRAM devices are placed in the self-refresh mode of operation.

- Halts all clocks, disable the PLL, disable the 14.7456 MHz oscillator, and de-assert the CLKEN output signal.

- Wait for IRQ or FIQ to be asserted (which will return the LH79520 to the Active mode).

When an IRQ or FIQ occurs, the LH79520 returns to the Active mode, restarts the output clocks (which may require a delay for the PLL to reacquire lock, if the PLL is in use), resumes SDRAM refresh and then cedes control of the AHB.

#### 3.6 ESD Considerations

The LH79520-10 Card Engine was designed to interface to a customer's peripheral board. The Card Engine was designed to be low cost and adaptable to many different applications. The LH79520-10 Card Engine does not provide any ESD protection circuitry on the card and must be provided by the product it is used in. Logic has extensive experience in designing products with ESD requirements. Please contact Logic if you need any assistance in ESD design considerations.

## 4 Memory & I/O Mapping

## 4.1 SDRAM Memory Map

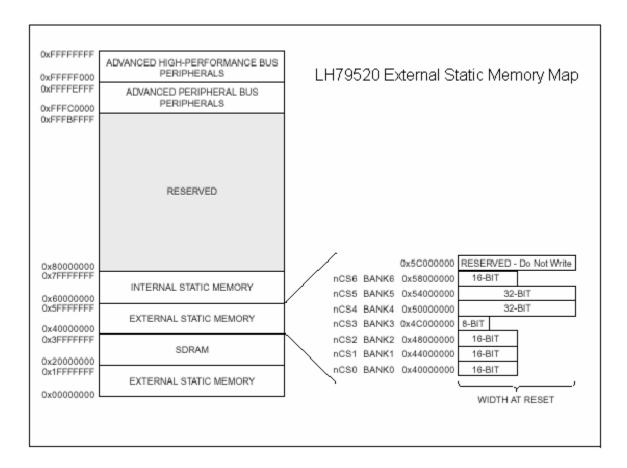

## 4.2 External Static Memory Map

#### 4.2.1 Card Engine Static Memory Map Description

The table below indicates what each bank of external static memory is being used for on the card engine.

| Chip Select | Bank | Start Address | Memory Description                             |

|-------------|------|---------------|------------------------------------------------|

| nCS6        | 6    | 0x5800 0000   | N/A <sup>1</sup>                               |

| nCS5        | 5    | 0x5400 0000   | IO Controller Peripherals (fast <sup>2</sup> ) |

| nCS4        | 4    | 0x5000 0000   | IO Controller Peripherals (slow <sup>2</sup> ) |

| nCS3        | 3    | 0x4C00 0000   | Boot Device (flash or EEPROM <sup>3</sup> )    |

| nCS2        | 2    | 0x4800 0000   | open                                           |

| nCS1        | 1    | 0x4400 0000   | Video <sup>3</sup>                             |

| nCS0        | 0    | 0x4000 0000   | Boot Device (flash or EEPROM <sup>3</sup> )    |

#### Notes:

- 1. Pin nCS6 is used as an alternate pin function.

- 2. IO Controller peripherals are those components that get a decoded chip select from the IO Controller. (i.e. CPLD memory mapped registers, onboard SMSC 91C111 Ethernet controller, etc... Please see the LH79520-10 IO Controller Specification document for details.) These

peripherals are separated into two different chip select banks, due to difference in timing: slow and fast.

Logic PN: 70000014

3. Components planned for future applications.

## 4.2.2 Chip Select 4 (nCS4) – IO Controller Peripherals (slow timing)

The table below indicates how the IO Controller decodes chip select 4. For more detailed information see the IO Controller Interface Specification.

| Chip Select | Address Range             | Memory Description       | Size         |

|-------------|---------------------------|--------------------------|--------------|

| nCS4        | 0x5000 0000 – 0x501F FFFF | open                     | 2MB          |

| nCS4        | 0x5020 0000 – 0x503F FFFF | CF Chip Select           | 2MB          |

| nCS4        | 0x5040 0000 – 0x505F FFFF | ISA-like Bus Chip Select | 2MB          |

| nCS4        | 0x5060 0000 – 0x51FF FFFF | open                     | 2MB<br>(X13) |

| nCS4        | 0x5200 0000 – 0x53FF FFFF | reserved                 | 1MB<br>(X32) |

## 4.2.3 Chip Select 5 (nCS5) – IO Controller Peripherals (fast timing)

The table below indicates how the IO Controller decodes chip select 5. For more detailed information see the IO Controller Interface Specification.

| Chip Select | Address Range             | Mem Block Description      | Size         |

|-------------|---------------------------|----------------------------|--------------|

| nCS5        | 0x5400 0000 – 0x541F FFFF | Wired LAN Chip Select      | 2MB          |

| nCS5        | 0x5420 0000 – 0x543F FFFF | Wired LAN Control Reg      | 2MB          |

| nCS5        | 0x5440 0000 – 0x545F FFFF | CODEC I2S Audio            | 2MB          |

| nCS5        | 0x5460 0000 – 0x547F FFFF | SPI Data Reg               | 2MB          |

| nCS5        | 0x5480 0000 – 0x549F FFFF | SPI Control Reg            | 2MB          |

| nCS5        | 0x54A0 0000 – 0x54BF FFFF | EEPROM SPI Reg             | 2MB          |

| nCS5        | 0x54C0 0000 – 0x54DF FFFF | Interrupt/Mask Reg         | 2MB          |

| nCS5        | 0x54E0 0000 – 0x54FF FFFF | Mode Reg                   | 2MB          |

| nCS5        | 0x5500 0000 – 0x551F FFFF | Flash Reg                  | 2MB          |

| nCS5        | 0x5520 0000 – 0x553F FFFF | SDRAM Reg                  | 2MB          |

| nCS5        | 0x5540 0000 – 0x555F FFFF | IO Controller Revision Reg | 2MB          |

| nCS5        | 0x5560 0000 – 0x557F FFFF | Extended GPIO Reg          | 2MB          |

| nCS5        | 0x5580 0000 – 0x55FF FFFF | open                       | 2MB (X5)     |

| nCS5        | 0x5600 0000 – 0x57FF FFFF | reserved                   | 1MB<br>(X32) |

## 5 Pin Descriptions & Functions

**IMPORTANT NOTE:** The following pin descriptions and states are described after the initialization of the LogicLoader<sup>TM</sup> (bootloader). Many of the signals defined in the tables below can be configured as input or outputs, active low or active high, and have different functions. It is critical to review all signals in the final design (both electrical and software) to verify the necessary configuration (external pull ups/pull downs).

In addition, keep in mind that the following mode line numbers on the card engine do not necessarily line up with the mode line numbers on the processor.

## 5.1 J1C Connector SODIMM 144-Pin Descriptions

| Pin# | Signal Name    | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------|----------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | ETHER_RX(-)    | ı   | This input pair receives 10/100 MB/s Manchester encoded data from the 10/100 BASE-T receive lines.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2    | MSTR_nRST      | I/O | This signal initiates a hard reset – external memory contents are lost during reset. This signal is active low. A low on this signal resets the Card Engine. This signal has a 10k pull up located on the Card Engine.                                                                                                                                                                                                                                                                                                    |

| 3    | ETHER_RX(+)    | ı   | This input pair receives 10/100 MB/s Manchester encoded data from the 10/100 BASE-T receive lines.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 4    | uP_SW_nRESET   | ı   | This signal initiates a soft reset – external memory contents are retained during reset. This signal is active low. The uP_SW_RESET signal is an input to the IO Controller. When a low pulse is detected, the IO Controller generates an interrupt to the microcontroller. The microcontroller then reads the interrupt/mask register of the IO Controller, which indicates a soft reset has been administered. See the IO Controller Interface Specification. This signal has a 10k pull up located on the Card Engine. |

| 5    | ETHER_TX(-)    | 0   | This output pair drives 10/100 Mb/s Manchester-encoded data to the 10/100 BASE-T transmit lines.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6    | FAST_nMCS      | 0   | Chip select for area 5 of LH79520 memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 7    | ETHER_TX(+)    | 0   | This output pair drives 10/100 Mb/s Manchester-encoded data to the 10/100 BASE-T transmit lines.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 8    | SLOW_nMCS      | 0   | Chip select for area 4 of LH79520 memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 9    | DGND           | I   | Digital Ground (0V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 10   | VIDEO_nMCS     | 0   | Chip select for area 1 of LH79520 memory (active low).                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 11   | ETHER_nACT_LED | 0   | This output indicates transmission or reception of frames or detection of a collision. This signal may be connected to an external LED.                                                                                                                                                                                                                                                                                                                                                                                   |

| 12   | BOOT_nMCS      | 0   | This signal is the chip select for boot ROM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 13   | ETHER_nLNK_LED | 0   | This output indicates valid link pulses. May be connected to an external LED.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 14   | nIOWR          | 0   | This signal is driven by the ISA bus master or DMA controller to request an I/O resource to accept data from data lines.                                                                                                                                                                                                                                                                                                                                                                                                  |

| 15   | nSTANDBY       | ı   | CPU power mode signal. This signal is connected to the LH79520 on pin #99 (PF1/CLKEN). This signal has a 10k pull up located on the Card Engine.                                                                                                                                                                                                                                                                                                                                                                          |

| 16   | nIORD          | 0   | This signal is driven by the ISA bus master or DMA controller to request an I/O resource to drive data onto the data bus during the cycle.                                                                                                                                                                                                                                                                                                                                                                                |

| 17   | DGND           | I   | Digital Ground (0V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 18   | 3.3V_WRLAN     | ı   | This pin outputs power for use with external Wired Lan circuitry. Please refer to Logic Product Development SDK and IDK kits for reference designs for Wired Lan connector implementations. Typically this power output would be used to supply power to the Wired Lan Activity and Link LEDs.                                                                                                                                                                                                                            |

| 19   | 3.3V           | I   | Power Supply (3.3V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 20   | BALE           | 0   | This signal is driven to a logical one to indicate when the MA<19:0> signal lines are valid.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Pin #   | Signal Name       | I/O      | Description                                                                                                                                          |  |  |

|---------|-------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| F 111 # | Signal Name       | 1/0      | The NMI (non-maskable interrupt – highest priority) and IRQ[3:0] signals                                                                             |  |  |

|         |                   |          | generate a request to the CPU for service (interrupt service routine). The NMI                                                                       |  |  |

|         |                   |          | signal is active low. The uP_NMI has a 10k pull up located on the Card                                                                               |  |  |

| 21      | uP_NMI            | I        | Engine.                                                                                                                                              |  |  |

|         |                   |          | The I/O channel ready signal line allows the resources to indicate to the ISA                                                                        |  |  |

| 00      | OLIDBY            | ١.       | bus master that additional cycle time is required. This signal has a 1k pull up                                                                      |  |  |

| 22      | nCHRDY            | 1        | located on the Card Engine.                                                                                                                          |  |  |

| 23      |                   | NC       | No internal connection. DO NOT TIE TO GND. LEAVE FLOATING.                                                                                           |  |  |

|         |                   |          | Reserved for Production Test: This signal is tied low internally by the                                                                              |  |  |

| 24      | uP_TEST1          | 1        | processor. No external connection is necessary. LOW indicates NORMAL operation.                                                                      |  |  |

|         | ur_12011          | <u> </u> | Hardware interrupt on LH79520 (active low). Optionally configured as LH79520                                                                         |  |  |

| 1       |                   |          | general-purpose input. The uP_IRQC signal has a 10k pull up located on the                                                                           |  |  |

| 25      | uP_IRQC           | 1        | Card Engine.                                                                                                                                         |  |  |

|         |                   |          | Reserved for Production Test: This signal is tied low in the processor. LOW                                                                          |  |  |

| 26      | uP_TEST2          | - 1      | indicates NORMAL operation, pull up to enable the use of a JTAG emulator.                                                                            |  |  |

|         |                   |          | Hardware interrupt on LH79520 (active low). Optionally configured as LH79520                                                                         |  |  |

| 07      |                   | ١.       | general-purpose input. The uP_IRQB signal has a 10k pull up located on the                                                                           |  |  |

| 27      | uP_IRQB           | <u> </u> | Card Engine.                                                                                                                                         |  |  |

| 28      | uP_nTRST          | 1        | JTAG Test Reset Input. This signal has a 10k pull up located on the card engine.                                                                     |  |  |

| 20      | ur_iiikoi         | <b>'</b> | Hardware interrupt on LH79520 (active low). Optionally configured as LH79520                                                                         |  |  |

|         |                   |          | general-purpose input. The uP_IRQA signal has a 10k pull up located on the                                                                           |  |  |

| 29      | uP_IRQA           | - 1      | Card Engine.                                                                                                                                         |  |  |

|         |                   |          | JTAG Test Mode Select Input. This signal has a 10k pull up located on the                                                                            |  |  |

| 30      | uP_TMS            | - 1      | card engine.                                                                                                                                         |  |  |

| 31      |                   | NC       | No internal connection. DO NOT TIE TO GND. LEAVE FLOATING.                                                                                           |  |  |

|         |                   |          | JTAG Test Data Serial Output. This signal has a 10k pull up located on the                                                                           |  |  |

| 32      | uP_TDO            | 0        | card engine.                                                                                                                                         |  |  |

| 33      |                   | NC       | No internal connection. DO NOT TIE TO GND. LEAVE FLOATING.                                                                                           |  |  |

| 0.4     | D TD:             | ١.       | JTAG Test Serial Data Input. This signal has a 10k pull up located on the card                                                                       |  |  |

| 34      | uP_TDI            | 1        | engine.                                                                                                                                              |  |  |

| 35      |                   | NC       | No internal connection. DO NOT TIE TO GND. LEAVE FLOATING.                                                                                           |  |  |

| 36      | UD TOK            | ١,       | JTAG Test Clock Input. This signal has a 10k pull up located on the card                                                                             |  |  |

| 30      | uP_TCK            | <u> </u> | engine.                                                                                                                                              |  |  |

|         |                   |          | The WAIT signal requests the current bus cycle be extended by one or more wait states (active low). The uP_nWAIT signal has a 10k pull up located on |  |  |

| 37      | uP_nWAIT          | 1        | the Card Engine.                                                                                                                                     |  |  |

|         |                   |          | Boot select signal (0 = external boot PROM, 1 = onboard flash) This signal                                                                           |  |  |

| 38      | uP_MODE3          |          | has a 10k pull up located on the Card Engine.                                                                                                        |  |  |

| 39      |                   | NC       | No internal connection. DO NOT TIE TO GND. LEAVE FLOATING.                                                                                           |  |  |

| 40      | uP_MODE2          | ı        | This signal has a 10k pull up located on the Card Engine.                                                                                            |  |  |

| 41      |                   | NC       | No internal connection. DO NOT TIE TO GND. LEAVE FLOATING.                                                                                           |  |  |

| 42      | uP_MODE1          | I        | This signal has a 10k pull up located on the Card Engine.                                                                                            |  |  |

| 43      | uP_UARTA_TX - PA4 | 0        | Transmitter serial data output.                                                                                                                      |  |  |

| 44      | uP_MODE0          | I        | This signal has a 10k pull up located on the Card Engine.                                                                                            |  |  |

|         |                   |          | Receiver serial data input. This signal has a 10k pull up located on the Card                                                                        |  |  |

| 45      | uP_UARTA_RX - PA3 | I        | Engine.                                                                                                                                              |  |  |

| 46      |                   | NC       | No internal connection.                                                                                                                              |  |  |

| 47      |                   | NC       | No internal connection.                                                                                                                              |  |  |

| 48      |                   | NC       | No internal connection.                                                                                                                              |  |  |

| 49      |                   | NC       | No internal connection.                                                                                                                              |  |  |

| 50      |                   | NC       | No internal connection.                                                                                                                              |  |  |

|         | I.                | 1        | 1                                                                                                                                                    |  |  |

| Pin#   | Signal Name    | I/O | Description                                                                                                                                    |  |

|--------|----------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PIII # | Signal Name    | 1/0 | ·                                                                                                                                              |  |

| 51     | nSUSPEND       | ı   | CPU power mode signal. This signal is connected to the LH79520 on pin #99 (PH5/nCS6) This signal has a 10k pull up located on the Card Engine. |  |

| 52     |                | NC  | No internal connection.                                                                                                                        |  |

| 53     | uP_AUX_CLK     | 0   | This auxiliary clock is controlled in the CPU and can be used by the peripherals.                                                              |  |

| 54     | uP_DACK1       | 0   | This handshake signal is output by the CPU to acknowledge DMA requests.                                                                        |  |

| 55     | DGND           | ı   | Digital Ground (0V)                                                                                                                            |  |

| 56     |                | NC  | No internal connection.                                                                                                                        |  |

| 57     | VCORE          | I   | CPU core voltage supply (on during low power, SW_Reset).                                                                                       |  |

| 58     | VCORE          | - 1 | CPU core voltage supply (on during low power, SW_Reset).                                                                                       |  |

| 59     | VCORE          | I   | CPU core voltage supply (on during low power, SW_Reset).                                                                                       |  |

| 60     | VCORE          | I   | CPU core voltage supply (on during low power, SW_Reset).                                                                                       |  |

| 61     | 3.3V_uP_SDRAM  | ı   | uP and SDRAM Power Supply (3.3 V) (on during low power, uP_SW_Reset)                                                                           |  |

| 62     | 3.3V_uP_SDRAM  | I   | uP and SDRAM Power Supply (3.3 V) (on during low power, uP_SW_Reset)                                                                           |  |

| 63     | 3.3V_uP_SDRAM  | 1   | uP and SDRAM Power Supply (3.3 V) (on during low power, uP_SW_Reset)                                                                           |  |